한자 : 論理回路

영어 : Logic circuit

1 정의

부울 대수를 이용하여 1개 이상의 논리 입력을 일정한 논리 연산에 의해 1개의 논리 출력을 얻는 회로

전자회로의 구성요소들을 이용하여 만든 논리 게이트(NAND, NOR, NOT 등)를 이용해 원하는 동작을 구현하는, 현대의 디지털 시대를 이끈 장본인 격의 학문이다.

2 교과목

Digital Logic Circuit 또는 Logic Design

공대 전기전자공학부 및 컴퓨터공학부의 전공 과목 중 하나이다. 디지털공학이라고도 한다. 논리 연산의 방법과 현대의 디지털 회로에 쓰이는 여러가지 개념 및 적용법을 배우는 과목이다. 이 과목에선 기본적으로 입력값과 출력값이 0 과 1로 구성되어 있기 때문에 접근 방식이 기존에 학생들이 배우던 아날로그 방식과는 확연히 다르며[1] 아날로그 회로를 생각하고 이 과목을 듣게 되면 곤란해진다.

기본적인 접근 방식이 부울 대수이기 때문에 집합을 생각하면 쉽다. 그러나 사실 이 과목은 엄밀히 말하면 논리 연산의 방법 자체를 배우는 것에 중점을 두기 보다는 디지털 회로에 쓰이는 개념들에 더 중점을 두는 과목이기 때문에 앞부분을 잘한다고 뒷부분까지 잘하게 된다는 보장은 없다. 특히 이 과목은 교수의 재량권이 매우 큰 과목이고, 딱 어디까지가 디지털 논리회로고 어디부터가 디지털 시스템 설계인가 하는 명확한 기준이 없다. 따라서 교수에 따라서도 공부량이 좌우될 수 있는 과목.

일반적으로 전기전자공학부와 컴퓨터공학부의 1,2학년 또는 3학년 학생들이 주로 배우게 되며 당연하게도 전공기초인 학교가 많기 때문에 웬만한 전자공학도라면 한번쯤은 듣게 되는데 앞부분은 몰라도 뒷부분에서 상당히 머리가 아픈 개념들이 많이 나오기 때문에 원서는 아니더라도 적어도 한글로 된 책을 방학 동안에 한번쯤은 읽어보는 것이 좋다.

2.1 내용

논리회로의 접근 방식은 크게 Combinational Logic Design(조합 논리, Structural Design)과 Sequential Logic Design(순차 논리, Behavioral Design)의 2가지로 나누어지게 되는데 쉽게 풀어쓰자면 Combinational Logic은 시간의 개념과 관계가 없는 논리 회로를 뜻하고 Sequential Logic은 시간의 개념이 포함된 논리 회로를 뜻한다.

이 문서는 Randy H. Katz가 지은 Contemporary Logic Design 2판을 기초로 작성하였다. 전문대학에서는 이보다 쉬운 교수 자체 집필교재를 사용한다.

2.1.1 Combinational Logic

- 부울 대수와 논리 연산 방법

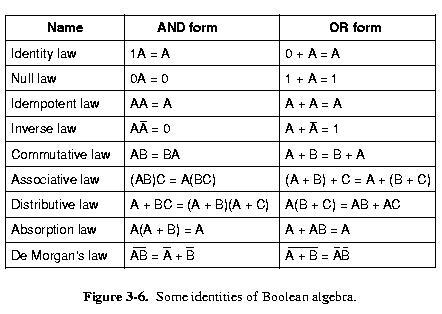

기본적인 논리 연산 방법에 대해 배우는 단원으로 논리 연산 자체는 딱히 중요하게 배우지는 않으나 어찌됐든 논리 회로 해석의 가장 기본이 되는 부분이므로 잘 공부해 놓는 것이 좋다. Truth table 해석법 및 SOP form과 POS form의 차이점 구별 및 적용 방법에 대해 공부하게 되며 더 나아가 Karnaugh Map(통칭 K-map)을 이용하여 여러 Boolean equation들을 줄이는 방법에 대해서도 공부하게 된다.

- Combinational Logic의 정의

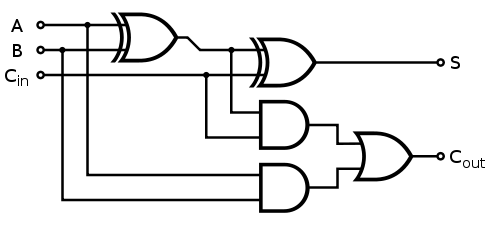

Adder의 개념이 처음으로 나오는 단원으로 여러 종류의 Adder와 기타 Combinaional Logic들을 K-map, Quine-McCluskey Method, Espresso 등 여러가지 방법으로 분석해보게 된다. 이 분석 결과들을 바탕으로 Hazard(0-hazard / 1-hazard)의 개념, 존재 여부 및 Hazard-free한 설계 방법에 대해서도 공부하게 된다.

- Combinational Logic의 적용법

Combinational Logic의 실질적인 적용법에 대해서 배우는 단원이다. ROM의 정의와 Multiplexor(MUX)및 Demultiplexor(DEMUX)의 작동원리 및 Multi-level로 구성된 MUX와 DEMUX 설계 방법(Cascading)에 대해서 공부하게 되며, 더 나아가 지금까지 배웠던 Combinational Logic을 실질적으로 설계하는 효율적인 방법들인 PAL과 PLA가 무엇인지에 대해서도 공부하게 된다. Tri-state의 개념에 대해서 처음으로 나오는 단원이기도 하다.

- Combinational Logic Design

위의 모든 적용법까지 다 배웠다면 이제 설계를 배울 차례만 남았다. 교수의 재량권이 매우 커지는 단원으로 어떤 방식의 설계를 가르치냐에 따라 난이도가 극명하게 갈리기 때문에 다양한 케이스들에 대해 제대로 숙지를 하고 있어야 공부하는데에 도움이 된다, Signed number와 2's complement의 개념에 대해서 배우게 되며 이를 바탕으로 위에서 했던 Adder를 응용한 Adder/Subtractor 및 Ripple-Carry Adder, Carry-Select Adder, Carry-Lookahead Adder 등등 Adder의 다양한 설계 방법에 대해 공부하게 되며 더 나가면 기초적인 ALU 설계 방법에 대해서도 공부하게 된다.

2.1.2 Sequential Logic

- Sequential Logic의 정의

Sequential Logic은 기본적으로 Memory와 위에서 배웠던 Combinational logic에 시간 개념을 넣어주는 것을 바탕으로 시작하며, 이 단원에서는 위에서 배운 게이트들을 이용하여 Memory를 어떤 식으로 구현하는지부터 시작한다. 이 단원에선 Sequential Logic의 기본 요소들인 Latch와 Flip-flop, Clock이 무엇인지 공부하며 다양한 형태의 Latch(R-S Latch, M-S Latch)와 Flip-flop(J-K Flip-flop, D Flip-flop, Edge-triggered Flip-flop)의 기본적인 구조에 대해서도 공부하게 된다. 그리고 이것들을 바탕으로 register의 개념 및 간단한 Shift register 설계방법에 대해서도 공부할 것이다. 이 단원부터는 기본적으로 시간의 개념이 들어가기 때문에 수많은 waveform들을 보게 될 것이며, 각 waveform에서 나타나는 특성들을 꼼꼼히 봐야한다는 것을 명심해야 한다.

- Finite State Machine

Finite State Machine(FSM)은 Sequential Logic의 설계에 쓰이는 수학적인 모델로써 특정 시간 당 단 하나의 state만을 갖고, 외부에서 입력된 어떤 event에 의해 state가 변화되는 형태의 모델을 의미한다. 이 단원에서는 이 FSM의 개념을 이용하여 Counter와 다양한 Behavioral Model(자판기, 에어컨, 신호등 등)을 어떤 방식으로 접근할 것인지에 대해 주로 공부하게 된다. 그리고 이 FSM의 설계 방식인 Moore machine(출력값이 현재의 state에만 의존하는 FSM)과 Mealy machine(출력값이 현재의 state와 입력값에도 의존하는 FSM)을 배우고 이를 바탕으로 다양한 State diagram을 그려보며 전체적인 설계의 접근 방법에 대해서 공부하게 된다.

- State Optimization

State의 수가 많다는 것은 필요한 메모리가 많다는 것을 의미하고 이는 곧 제품의 가격 및 설계의 복잡도에 악영향을 미친다. 따라서 State의 수를 최대한 줄이는 것은 논리 회로 설계에 있어서 가장 필수적인 부분 중 하나이다. 이 단원에서는 위에서 배웠던 FSM의 state를 최대한 줄일 수 있는 실질적인 방법에 대해서 공부하게 된다. 주로 Implication Chart를 이용하여 설계한 FSM의 state를 줄여보는 방법을 연습하게 되며 One-Hot 및 Heuristic algorithm을 이용한 가장 효율적인 state 할당에 대해서도 공부하게 된다.

- Sequential Logic Design

논리회로의 마지막 단원으로 HDL을 이용한 실제적인 설계방법을 배우게 된다. Sequential Logic을 무엇부터 설계해야하는지에 대한 단계적 접근법을 배우게 되며 전체적인 청사진인 FSM부터 시작해 세세한 clock이나 register를 어떤 방식으로 설계하느냐에 따른 장단점을 자세하게 배울 수 있다.

3 연관되는 교과목

- 디지털 시스템 설계

- 컴퓨터 구조

4 관련 문서

이후 내용 추가 바람- ↑ 비록 최근에는 기기의 소형화 및 정밀화 때문에 혼성 신호 모델이 각광을 받고 있긴 해도 이 과목을 배우는 사람은 대부분의 경우 어디까지나 학부생이라는 점을 알아둘 필요가 있다.